| |

Radim Visinka, Leos Chalupa, Ivan Skalka

Введение в архитектуру Cortex-M3. Часть I

Односкристалльные решения, выполненные на основе встроенных ARM-процессоров находят свое применение в самых различных областях рынка, включая такие ресурсоемкие сегменты как корпоративные приложения, автомобильные системы, домашние и беспроводные сетевые технологии и многие прочие.

Семейство процессоров на базе архитектуры ARM Cortex обеспечивают необходимые ресурсы для решения такого широкого круга задач.

Семейство процессоров Cortex включает в себя три основных подсемейства архитектуры ARMv7: подсемейство А для очень ресурсоемких приложений, выполняемых под управлением сложных операционных систем; подсемейство R для применения в системах реального времени; и подсемейство М, оптимизированного для применения в недорогих встроенных приложений.

Процессоры семейства Cortex-M3 — первые ARM процессоры, базирующейся на архитектуре ARMv7-М, которые были специально спроектированы для достижения высокой производительности всей системы в недорогих высокоэкономичных встроенных приложениях,таких как, например, системы промышленного контроля, автомобильная электроника, проводные и беспроводные телекоммуникационные системы, системы управления электроприводами и т.п. Для достижения этой цели было внесено множество изменений в базовую архитектуру, в частности, существенно упрощен процесс создания программного кода, что сделало рентабельным применение процессоров на базе архитектуры Cortex-M3 даже в самых простых приложениях.

Для увеличения производительности системы, процессоры должны работать либо с более высокой тактовой частотой либо использовать более изощренные методы увеличения эффективности вычислений. Повышение тактовой частоты в принципе может увеличить производительность, но в то же время увеличивает энергопотребление и сложность применения. С другой стороны, повышение эффективности вычислений при более низкой тактовой частоте значительно более предпочтительно. В основе процессора на базе архитектуры Cortex-M3 лежит ядро, выполненное по Гарвардской технологии с 3-ступенчатым конвейером, что обеспечивает такие привлекательные возможности, как предсказание переходов, однотактное умножение и аппаратно реализованное деление, что обеспечивает производительность порядка 1.25 MIPS/МГц (в тесте Drystone).

В процессорах Cortex-M3 реализован новый набор команд Thumb ® -2, что позволяет достигнуть на 70 % большей производительности на мегагерц, чем классические ARM процессоры на базе ARM7TDMI-S, использующие классический набор команд Thumb, и на 35 % более производительности, чем те же процессоры, выполняющие базовый набор команд ARM (по данным того же теста Drystone).

Сокращение времени выхода конечного продукта на рынок и снижение затрат на разработку являются важнейшими критериями при выборе процессора, точно так же как возможность быстро и легко создавать программный код является одним из ключевых требований в этом вопросе.

Процессоры на базе архитектуры Cortex-M3 разрабатывались с целью обеспечить как можно более быстрое и простое создание эффективного программного кода без использования ассемблерных вставок, при этом от программиста не должно было требоваться очень глубокого знания особенностей архитектуры процессора для создания приложений средней сложности. Данные процессоры используют упрощенную стековую модель программирования, в которой удалось совместить стандартные команды ARM с несколько переработанными и адаптированными к ядру ARM идеями, применявшимися в 8- и 16-разрядных микроконтроллерах, доказавшими свою высокую эффективность. В то же время аппаратно реализованное управление прерываниями позволяет создавать очень простые обработчики прерываний без использования ассемблерных вставок или какихлибо манипуляций с регистрами.

Новой, ключевой особенностью системы команд Thumb-2 является более эффективная реализация компилятора языка С с возможностью операций с битами и битовыми полями, аппаратным делением и более эффективной реализацией конструкций условий типа if/then. С точки зрения разработчика программного кода, процессоры с набором команд Thumb-2 позволяют создавать код намного быстрее, проще и эффективнее. Более того, при использовании набора команд Thumb-2 и соответствующего компилятора, больше не придется делать мучительный выбор между оптимизацией кода по скорости или по объему — в новых компиляторах возможна оптимизация как по объему, так и по скорости. Это еще более ускоряет процесс разработки программного кода, так как теперь программистам нет нужды заранее компилировать критические участки кода и прилинковывать их к основной программе в виде библиотек.

Постоянным ограничением в применении более производительных процессоров является их стоимость. Современные технологии производства являются дорогостоящими и поэтому решающим моментом в уменьшении стоимости процессора является площадь его кристалла. Процессоры, выполненные по технологии Cortex-M3 используют самое маленькое ядро ARM на сегодняшний день, содержащее всего 33 тысячи вентилей, выполненные по 0.18 мкм технологии, и уменьшенные до разумных размеров периферийные модули. Требования ядра к объему памяти также минимизированы за счет внедрения технологий хранения невыровненных данных, битовых операций и системы команд Thumb-2.

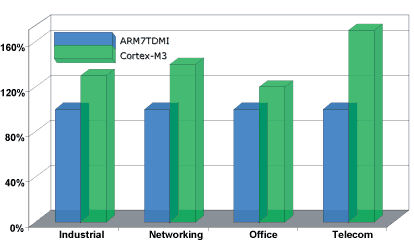

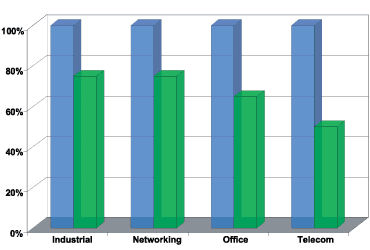

Эффект от этих нововведений выражается в более чем 25 % снижении требований к памяти по сравнению с классическими ARM процессорами. Сравнительные графики производительности и объема кода в различных областях применения приведены соответственно на рис. 1 и 2.

Рис. 1. Сравнение производительности процессоров ARM7DTMI и Cortex-M3 в различных приложениях

Рис. 2. Сравнение требуемого объема кода для процессоров ARM7DTMI и Cortex-M3 в различных приложениях

В последнее время процессоры на основе технологии ARM нашли широчайшее применение во множестве встраиваемых приложений. Процессоры на основе архитектуры CortexM3 являются дальнейшим и наиболее прогрессивным развитием классической архитектуры ARM и, по всей видимости, станут наиболее популярными в самое ближайшее время за счет более высокой производительности, менее сложной модели программирования, прекрасной системы обработки прерываний и низкой цены. Некоторые преимущества процессоров на базе архитектуры Cortex-M3 перед процессорами на базе классической архитектуры приведены в табл. 1.

Таблица 1. Сравнение ядер ARM7TDMI-S и Cortex-M3

| Параметр |

Ядро |

| ARM7TDMI-S |

Cortex-M3 |

| Ядро |

ARMv4T |

ARMv7-M |

| Архитектура |

фон Неймана |

Гарвардская |

| Поддерживаемые системы команд |

Thumb |

Thumb / Thumb-2 |

| Прерывания |

FIQ/IRQ |

NMI + от 1 до 240 физических прерываний |

| Время обработки прерывания |

24..42 тактов |

12 тактов |

| Пошаговый режим |

Нет |

Интегрирован |

| Защита памяти |

Нет |

8 региональных устройств защиты памяти |

| Производительность |

0.95 DMIPS/МГц (в режиме ARM) |

1.25 DMIPS/МГц |

| Потребляемая мощность |

0.28 мВт/МГц |

0.19 мВт/МГц |

| Площадь кристалла, мм2 |

0.62 (только ядро) |

0.86 (ядро и стандартная периферия) |

Заявления, подобные приведенным выше, могут на первый взгляд показаться голословными и необоснованными. В этом случае есть смысл ближе познакомиться с архитектурой Cortex-M3.

Процессор на базе архитектуры Cortex-M3 в своей основе имеет иерархическую структуру. Она включает в себя ядро CM3Core с развитой периферией, включающей в себя механизмы управления прерываниями, защиты памяти и внутрисхемной отладки и другие. Этот набор обладает прекрасной конфигурируемостью, что позволяет применять этот процессор для решения широкого спектра задач и наиболее полно отвечать требованиям, выдвигаемым к нему. Ядро Cortex-M3 и интегрированные в него компоненты (рис. 3) созданы с учетом требований к минимизации требуемого объема памяти и потребления энергии.

Рис. 3. Блок-схема ядра Cortex-M3

Ядро Cortex-M3 базируется на Гарвардской архитектуре и имеет раздельные шины для команд и для данных в отличие от стандартных ARM процессоров, использующих фон Неймановскую архитектуру и совмещенные шину и память как для данных, так и для команд.

Поскольку процессоры Cortex-M3 считывают данные и команды одновременно, это позволяет производить некоторые операции одновременно и таким образом существенно повысить производительность системы.

Встроенный в ядро конвейер имеет три стадии работы: выборка команды, декодирование команды, выполнение команды. Для случаев, когда в конвейере декодируется команда перехода, на стадии декодирования также производится выборка инструкции предсказания перехода, что также приводит к ускорению выполнения программы. Процессор выбирает команду назначения перехода во время собственно стадии декодирования. Позже, на стадии выполнения команд, переход разрешается и к этому моменту уже известно, какая команда будет следующей. В случае, если переход не производится, следующая последовательность команд и так уже доступна. В случае же, если переход производится, команда перехода становится доступной в то же время, когда собственно переход и разрешается, таким образом сводя время простоя к единственному такту.

Ядро процессора Cortex-M3 содержит декодер для традиционной системы команд Thumb и для новой системы Thumb-2, усовершенствованное АЛУ с поддержкой аппаратного умножения и деления, управляющей логикой и интерфейсами к другим компонентам системы.

Процессор на базе архитектуры Cortex-M3 представляет собой 32-разрядный процессор с 32-разрядными шиной данных, банком регистров и интерфейсом с памятью. Он содержит 13 регистров общего назначения, два указателя стека, регистр связей, счетчик команд, регистр статуса и множество специальных регистров.

Процессор на базе архитектуры Cortex-M3 поддерживает два режима работы, Thread и Handler, а также два уровня доступа к коду (привилегированный и непривилегированный), позволяющие создавать сложные открытые и при этом не жертвовать безопасностью. Непривилегированный уровень доступа ограничивает или полностью запрещает доступ и использование некоторых ресурсов типа определенных команд или областей памяти. Режим Thread является стандартным режимом работы и поддерживает распределение уровней доступа, тогда как режим Handler включается лишь в некоторых случаях и весь код получает привилегированный уровень доступа.

В следующих частях статьи мы подробно рассмотрим принципы распределение памяти, операции с битами, преимущества системы команд Thumb2 перед стандартной системой команд Thumb, работу контроллера прерываний, модуля защиты памяти, контроллеров шин и интерфейсов. Также будут рассмотрены принципы хранения невыровненных данных в памяти, режимы энергосбережения и, собственно, рассмотрим основные семейства процессоров на базе архитектуры Cortex-M3.

Павел Вовк

компания Элтис Компоненты

|